Experimental and Theoretical NANOTECHNOLOGY http://etn.siats.co.uk/

# Analysis of flip flop design using nanoelectronic single electron transistor

S. Rajasekaran<sup>\*</sup>, G. Sundari

*Faculty of Electronics Engineering, Sathyabama University, Chennai-600119, India* \*) *Email: srsekar7@gmail.com.*

Received 3 March 2015; Revised 26 Nov. 2015; Accepted 16 Feb. 2016

Single Electron Transistor (SET) is a nanoelectronic device that operates under the controlled mode of tunneled individual electrons. In this paper, a comparative analysis was performed employing SET based D-Flip flop with conventional logic D-flip flop. SET is eminent nanoscale devices that have low power dissipation, high speed and performance. The flip flop design was simulated using SIMON simulator and the stability of its operation was analyzed applying the Monte-Carlo method that represented stability with low power dissipation and matched the functionality of traditional CMOS devices.

**Keywords:** Logic circuits; Coulomb blockage; Nanoelectronics; Single electron device. **PACS:** 42.79.T; 73.23.Hk; 85.35p; 85.35.Gv.

# **1. Introduction**

The advancement of CMOS technology is still in back evolution and the increase in power utilization has become a main issue in the fabrication of large-scale integrated circuits. Consequently, the single-electron transistor (SET) has intrigued considerable attention because of its low power disbursement and high packing concentration. The information in the form of bits is represented by the presence or absence of single electrons at the quantum conducting islands. The fundamental principle of single-electronics is the Coulomb blockade was first observed and studied by Gorter [1].

It is widely known the size and transistor compactness facilitate vast improvement in the semiconductor based technology. Single-electron tunneling device [2] also has smart features like excellent current control, reduced dimensions and low noise behavior. These features should allow the realization of chips containing a number of the devices orders of magnitude greater than those indicated by the roadmap but still respecting the roadmaps area and power restrictions [3]. A variety of useful devices and concepts utilizing the single-electron tunneling features, such as, cellular automata, the binary decision device [4], and SET logic gates ie. OR,

AND, NAND, NOR, etc. [5,6], single electron memories [7], control-control-Not gate [8], analog to digital converter [9], stochastic associative memory [10] have been projected and experienced by actual devices.

The need for computer-aided design and simulation of single-electron circuits has long been recognized. Several simulators and simulation methods have been developed to support single-electron circuit design. SIMON is such a simulator developed by Wasshuber et al [11]. Fabrication of SEDs is an expensive and time-consuming process and, because of that, computer-aided design and simulation tools have been developed in order to study these circuits. A major improvement in SED circuits was achieved by the development of SIMON, which is a Monte Carlo-based tool capable to design, simulate and study SEDs and circuits.Up to date, SIMON has been used for various relevant studies and showed it is a proven tool for such a mission [12].

# 2. Single-Electron Tunnelling

#### 2.1 Coulomb blockade

Single-electron circuits consist of conducting quantum islands, tunnel junctions, capacitors, and voltage source. The quantum islands are subjectively connected between the tunnel junctions, capacitors and voltage sources. The movement of single electron charge through the tunnel junction is referred as tunnelling, where the electrons are tunnelled through a tunnel junction strictly one after another. This tunnel event of an electron is described by single electronics orthodox theory also a stochastic nature and the energy quantization is in discrete process. If the additional electrons are injected through the energy barrier of the insulating layer, it may prevent the system is said to be Coulomb blockade.

The basic principle of single electronics is that one needs coulomb energy  $E_C$  to charge an island with an electron. This energy is:

$$E_{\rm C} = e^2/2C \gg 2k_{\rm B}T \tag{1}$$

Where  $C_iC$  is the capacitance of the island, *e* is the elementary charge, k<sub>B</sub> is Boltzmann's constant and T is the absolute temperature [13]. Since the electric charge flows through the tunnel junctions in multiples of electrons. To assure that electron states are localized on islands all tunnel resistances must be larger than the fundamental quantum resistance

$$R_T > R_Q = h/e^2 \approx 25.813 \text{ K}\Omega$$

where h is Planck's constant.

To simulate in a single-electron circuit the tunnel event of electrons from island to island has to determine the rates of all possible tunnel events due to free energy changes. The free energy F, of a single-electron circuit is the differences of the electrostatic energy U, stored in its capacitances and the work done by the voltage sources of the single electron circuit W,

$$\mathbf{F} = \mathbf{U} - \mathbf{W} \tag{3}$$

The electrostatic energy is given by

(2)

$$U = \frac{1}{2} (q, v) \left(\frac{v}{q}\right) \tag{4}$$

where q and v are the unknown variables of the island charge and voltage matrices respectively, and Q and V are the known variables of the island charge and voltage matrices, respectively. The work done by the voltage sources is given by

$$W = \sum \int V_n(t) i_n(t) dt$$

(5)

where  $V_n(t)$  t) is the voltage of the  $n^{\text{th}}$  voltage source and  $i_n(t)$  t) is the current through the  $n^{\text{th}}$  voltage source. The tunnel rate r for a particular tunnel event is given by

$$\Gamma = \frac{\Delta F}{e^2 R_r \left[ 1 - \exp(-\frac{\Delta F}{kT}) \right]} \tag{6}$$

where  $\Delta F$  is the free energy change due to this tunnelling event,  $R_T$  is the tunnel resistance on the electron transported through tunnel junction, and  $k_BT$  is the thermal energy. Overall tunnel rates for all possible tunnel events is determined using a Monte Carlo method combined with an exponential distribution of tunnel events The time duration of a particular event is given by

$$\Delta t = -\frac{\ln(r)}{r} \tag{7}$$

#### 2.2. Monte Carlo Technique

Currently, two simulation approaches used in SET circuits. One is based on a Monte Carlo method, and the other on a Master equation Method. The Monte Carlo approach starts with all possible tunnel events, considered to be independent and exponentially distributed. Calculates their probabilities, and chooses one of the possible events randomly, weighted according to their probabilities. The Monte Carlo approach gives better transient and dynamic characteristics of SET circuits because its model the underlying microscopic physics. Tunnel events are modelled as discrete events as long as the electrons are confined on quantum dots.

#### 2.3. Single-Electron Transistor (SET)

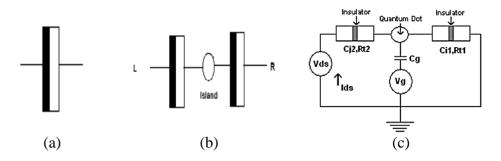

Single-electron Transistor is a Nanoelectronic device that used to monitor the electron tunnelling through the quantum island. SET consists of two tunnel junctions and a quantum island (quantum dot) about one nanometer range. The device structure just like MOS transistor, two junctions, as source and drain, instead of channel region the electrons can pass through the quantum island when reaches the coulomb energy. The effect of controlling the electron tunnel is coulomb blockade. The device can transfer the electrons from source to drain one by one under the application of gate voltage. So the tunnelling current is monitored by the voltage applied to the gate through a capacitor. This way charge carrier can transfer across the quantum island only after the sufficient voltage across the capacitor. Electron tunnelling rate based on the stochastic nature of the process takes place across the SET [15].

Figure. 1: (a) Schematic diagram for a tunnel junction, (b) Quantum dot island with two tunnel junctions, (c) Circuit diagram of the Single Electron Transistor.

## **3. Results and discussion** *3.1. Design of D-Flip-flop using Logic gates*

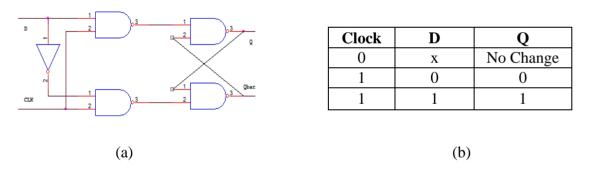

The flip-flop is a basic circuit to store state information from two stable states. It is the basic storage element in the sequential logic systems. The design of D-Flip flop circuit using Logic gates is shown in Fig. 2. This circuit is a memory element with two inputs of different logical combination input values. The D-FF consists of 4 NAND gates and one NOT gate, it consists of different logic function.

Figure. 2: (a) Diagram of the D-flip flop using Logic gates (b) Logic table.

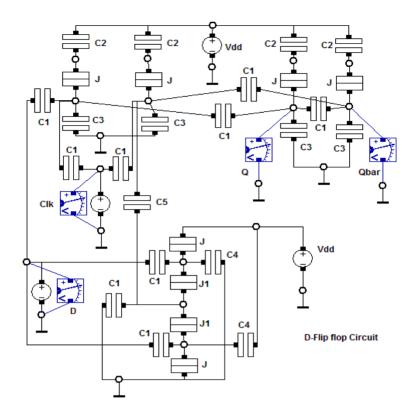

#### 3.2. Design of D-Flip-flop using SET

The D-Flip flop circuit design using single electron transistor is shown in Fig.3. Hence the circuit comprises thirteen islands, N1 to N13, bounded by eight tunnel junctions. The capacitance of each junction and their resistances are shown in Table 1. The circuit also comprises 7 capacitors, and the values of different for varying nodes. The two voltage sources  $V_{dd}$  are constant and its value is 0.16V. The input voltage and clock are applied to the D and Clock respectively through the capacitors C.

Figure. 3: Circuit diagram of single-electron D Flip flop.

The input voltage and Clock, shown in Fig. 3, are the inputs of the D-Flip flop named as D and Clk, and it takes only two values 0.0V which tends to the logic "1", and -0.1V which tends to the logic "0". The output signals of the D-Flip flop are taken from islands nodes named Q and Qbar respectively.

Table 1: Resistance and Capacitance values of Tunnel Junctions.

| Capacitance(F)              | Tunnel Junction(C,R) |                              |

|-----------------------------|----------------------|------------------------------|

| C1=5x10 <sup>-18</sup>      | T                    | $C_{j} = 1 \times 10^{-19}$  |

| $C2=11.7x10^{-18}$          | J                    | CJ =1X10                     |

| C3=9x10 <sup>-18</sup>      | J1                   | $C_{j1} = 5 \times 10^{-18}$ |

| $C4 = 4.25 \times 10^{-18}$ | JI                   | CJ1- 5x10                    |

| C5=1x10 <sup>-18</sup>      | R=1x10 <sup>5</sup>  |                              |

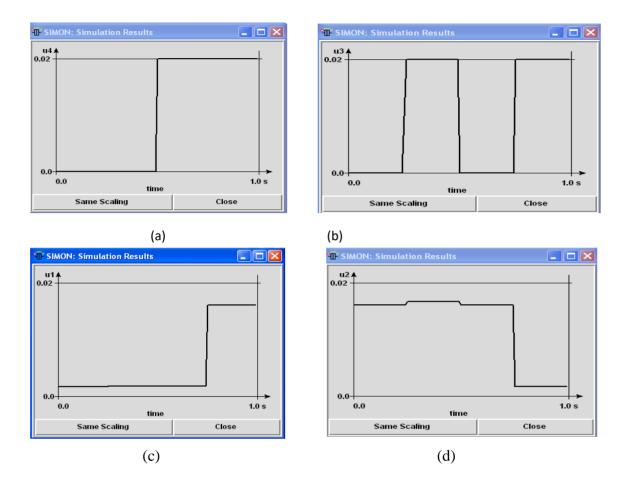

# 3.3. Analysis of Single-Electron D-Flip flop and Result

The single-electron D-Flip flop needs to be analysed the operational characteristics. From the corresponding output islands we take the outputs Q and Qbar respectively. The presence of zero voltage in the output islands corresponds to logic 1, whereas -0.1V voltage corresponds to logic 0. Hence, the input–output signals, of this D-Flip flop is shown in Fig. 4. The two inputs are D and clock and the two outputs Q and Qbar respectively.

When the input vector [00] is applied an excess electron is transported via tunnelling to island nodes and the island output voltage at Q and Qbar becomes 0.1V. When the input vector and

the clock signal are high, the electron tunnels out of nodes are charged according to the Fig. 4 given below.

Figure. 4. Operation of the single-electron D Flip flop (a) time variation of the input clock CLK; (b) time variation of the input voltage V, (c) time variation of the output charge Q and (d) time variation of the output charge Q-bar.

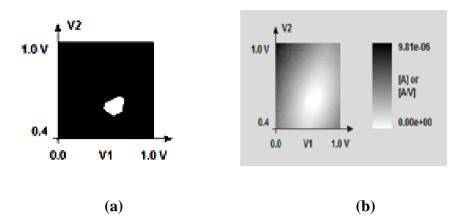

To confirm the stable operation of flip flop, its stability plot was constructed using SIMON. This plot is shown in figure 5. White regions correspond to completely stable state operation with an integer number of excess or missing electrons on the islands, whereas black regions correspond to completely unstable state operation. The gray regions correspond to less stable regions. The darker the gray region, the more unstable the gate operation. The slight instability in gate operation is apparent in Fig. 5, where slight charge fluctuations are observed.

Figure. 5: The stability plots of the single-electron D Flip flop.

#### 5. Conclusions

A single-electron D Flip flop was presented in this paper. This circuit produces their Q and Qbar. The circuit comprises 8 tunnel junctions, seven capacitors and thirteen islands. Each output is through the island and the presence of positive charge on it corresponds to the logic '1', whereas the absence of charge corresponds to the logic '0'. The energy history diagrams were plotted. The simulation procedure and the operational characteristics were verified. The circuit allowed less delay time, and power consumption reduction.

# References

[1] K. F. Goser, C. Pacha, A. Kanstein, M. L. Rossmann, Proc. IEEE 85 (1997) 558

[2] Grabert, Hermann, Michel H. Devoret, eds.Single charge tunneling: Coulomb blockade phenomena in nanostructures. **294**. Springer Science & Business Media, (2013)

[3] Likharev, Konstantin K., Proceedings of the IEEE 87 (1999) 606-632

[4] International technology roadmap for semiconductors (2012)

[5] Konstantin K. Likharev. Journal of Nanoelectronics and Optoelectronics, 3 (2008) 203

[6] C. J. Amsinck, N. H. Di Spigna, D. P. Nackashi, P. D. Franzon. Nanotechnology, 16 (2005) 2251

[7] Likharev K K. Hybrid, Proc. of Nanotech 5 (2007) 552

[8] S.H.Jo and W.Lu, IEEE Electron Device Letters 8 (2008) 392

[9] McNeil, R. P. G., et al. Nature 477 (2011) 439

[10] M. Kataoka, M. R. Astley, A. L. Thorn, D. K. L. Oi, C. H. W. Barnes, C. J. B. Ford, D. Andeson, G. A. C. Jones, I. Farrer, D. A. Ritchie, M. Pepper, Phys. Rev. Lett. **102** (2009) 56801 [11] Wasshuber, Christoph, Hans Kosina, and Siegfried Selberherr. Electron Devices, IEEE Transactions on **45** (1998) 2365

[12] Sergey Kubatkin, Andrey Danilov, MattiasHjort, JrmeCornil, JeanLucBrdas, NicolaiStuhr-Hansen, Per Hedegrd, Thomas Bjrnholm. Nature, **425** (2003) 698

[13] U. Hashim, A. Rasmi, S. Sakrani, Int. J. Nanoelectronics and Materials 1 (2008) 21

[14] TsimperidisIoannis, I. Karafyllidis, and AntoniosThanailakis.,Microelectronics Journal **35** (2004) 471

[15] Amit Chaudhry, JatindarNath Roy, Int. J. Nanoelectronics and Materials 4 (2011) 93

[16] AnbarasuPaulthurai, BalamuruganDharmaraj, Microelectronics and Solid State Electronics **4** (2012) 94

[17] Anbarasu.Paulthurai, Balamurugan.Dharmaraj, Int. J. Nanoelectronics and Materials 7 (2014) 149

© 2017 The Authors. Published by SIATS (<u>http://etn.siats.co.uk/</u>). This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (<u>http://creativecommons.org/licenses/by/4.0/</u>).